Bluespec Codesign Language: A Unified Language to Enable HW/SW Codesign

Nirav Dave SRI International

LAW December 6, 2011

#### Modern SoCs

Functionality is determined by power/energy issues

Hardware accelerated solutions consume dramatically less power than pure software solutions

$\Rightarrow$  Most SoC's have many specialized blocks

Many SoCs have to support full software stacks which at the bottom must interact with special purpose hardware efficiently

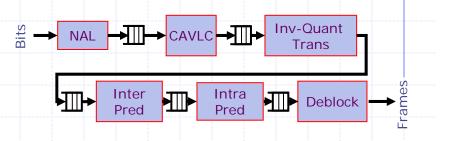

# Kinds of Hardware-Software Interactions

Hardware accelerators

H.264: any block can be implemented in HW or SW

Hardware calling software for functionality not supported in hardware

Software driving hardware as in testing or simulation

3

Different scenarios but similar problems

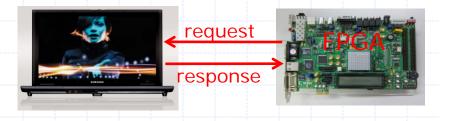

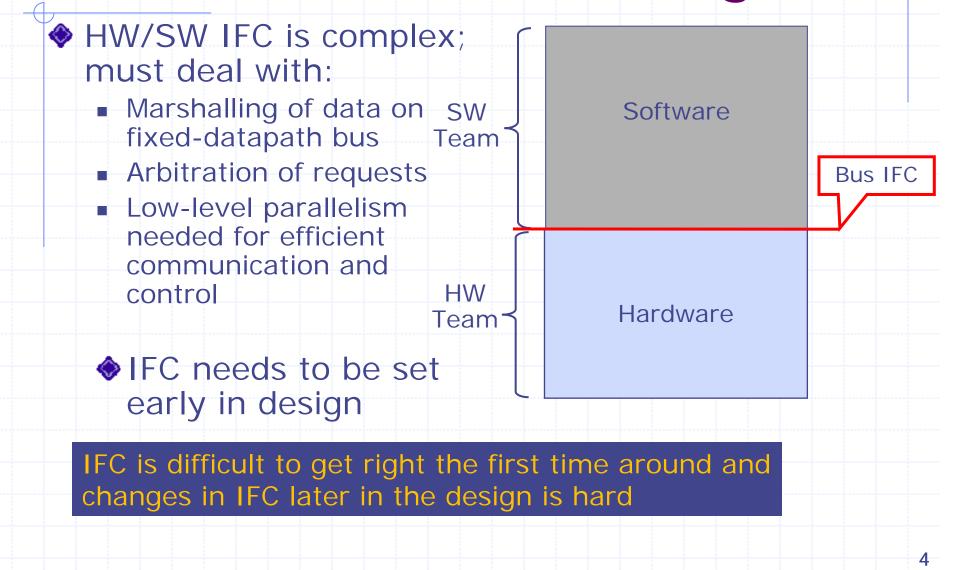

### Standard HW/SW Design

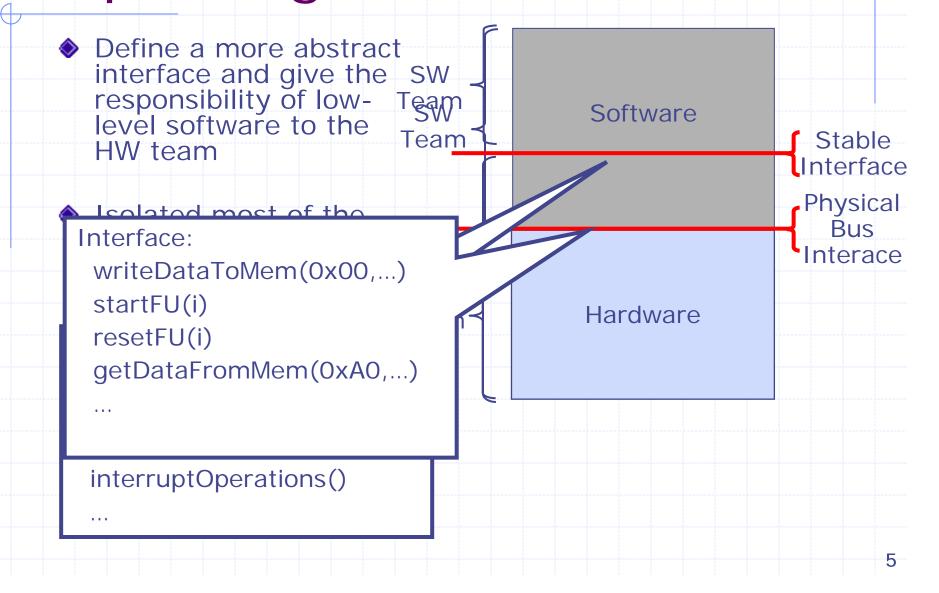

### Improving the Interface

#### The Real problem

- The issue is that HW and SW do not have the same underlying semantic model

- HW is gates and wires operating in parallel

- SW is a sequence of instructions

- This mismatch leads to this confusion and errors

- Also makes verification expensive and brittle

#### A unified Abstraction

- Represent HW and low-level SW in the same language:

- Both need fine grained parallelism

- "HW" team only has to deal with 1 language

- Provide tools to generate both hardware and software

- Consequences:

- Easy to move HW/SW boundary

- No data representation/ interfacing issues from semantic mismatch of C and RTL

- Complex bus interface is subsumed in a single language and can be abstracted cleanly

#### Panacea for HW-SW CoDesign

#### A compiler that takes

- A sequential program description

- Some performance, cost and power constraints

Automatically:

- Identifies what part should be implemented in HW

- Parallelizes HW part of design and parallelizes SW enough to exploit HW's parallelism

- Insert proper HW-SW communication channels between HW and SW

This is an unrealistic expectation – it is difficult to convey high-level performance goals, constraints, suitable microarchitectures and come up with appropriate partitions

# Our Goal: Facilitate Exploration

A single parallel language to express both HW and parallel SW parts of an algorithm

- Should be easy to express parallelism naturally

- Easy In-source specification of HW/SW partitioning

- Should be easy to change partitioning

- Designers should be able to reason about communication channel multiplexing directly in language.

- Compiler can easily separate the HW and SW compilation tasks and generate parts independently

Modularizes compilation and reasoning tasks

- Compiler should generate no-compromise hardware and high-quality software

Clean model for fast verification / testing

## Outline

Motivation Bluespec Codesign Language Compilation Partitioning Encapsulating the Bus Compilation Results Verification

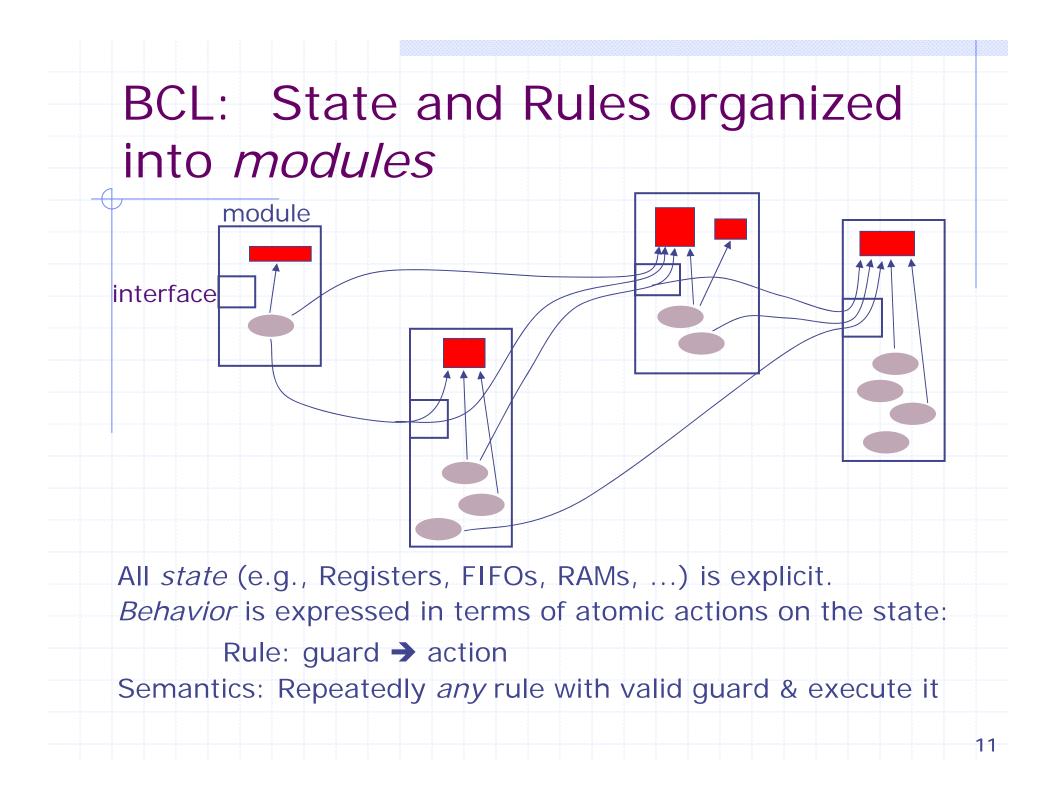

# Bluespec Codesign Language (BCL)

#### BCL is like Bluespec SystemVerilog (BSV)

- Conditionals, guards, and action composition

- Action and resource-level modularity

- Expressing nondeterminsm/parallelism comes naturally via rules

#### Extensions for efficient SW specification

- Sequential composition and looping constructs

- BCL designs are partitioned into HW and SW domains which can be compiled separately and then integrated

- HW translates to RTL via BSV Compiler

- SW converted to C++

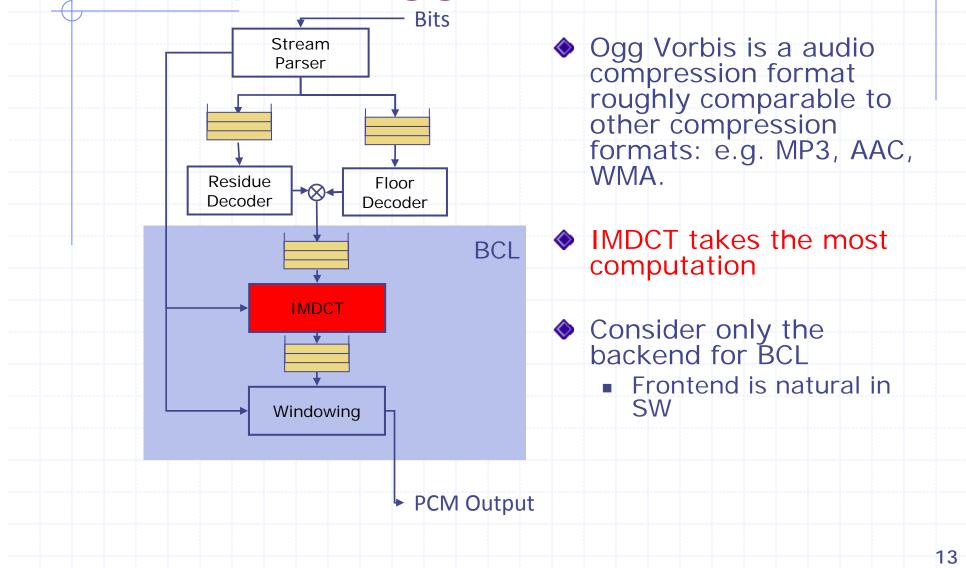

#### Example: Ogg Vorbis Decoder

#### A Closer look at IMDCT

```

Suppose we want to use

Array imdct(int N, Array vx){

hardware to accelerate

// preprocessing loop

FFT/IFFT computation

for(i = 0; i < N; i++){</pre>

vin[i] = convertLo(i,N_vx[i]);

vin[i+N] = convertHi(i,N,vx[i]);

// do the IFFT

vifft = ifft(2*N, vin);

// postprocessing loop

for(i = 0; i < N; i++){</pre>

int idx = bitReverse(i);

vout[idx] = convertResult(i,N,vifft[i]);

return vout;

```

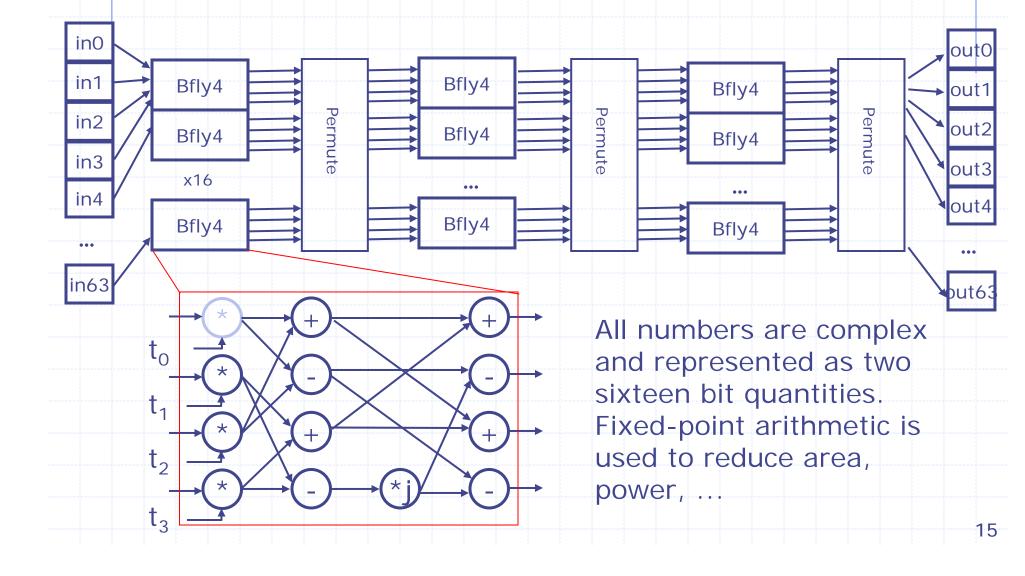

#### **Combinational IFFT**

#### 4-way Butterfly

function Vector#(4,Complex) bfly4 (Vector#(4,Complex) t, Vector#(4,Complex) k); Vector#(4,Complex) m, y, z; m[0] = k[0] \* t[0]; m[1] = k[1] \* t[1];m[2] = k[2] \* t[2]; m[3] = k[3] \* t[3];y[0] = m[0] + m[2]; y[1] = m[0] - m[2];y[2] = m[1] + m[3]; y[3] = i\*(m[1] - m[3]);Ζ m У z[0] = y[0] + y[2]; z[1] = y[1] + y[3];Polymorphic code: z[2] = y[0] - y[2]; z[3] = y[1] - y[3];works on any type of numbers for return(z); endfunction which \*, + and have been defined Note: Vector does not mean storage

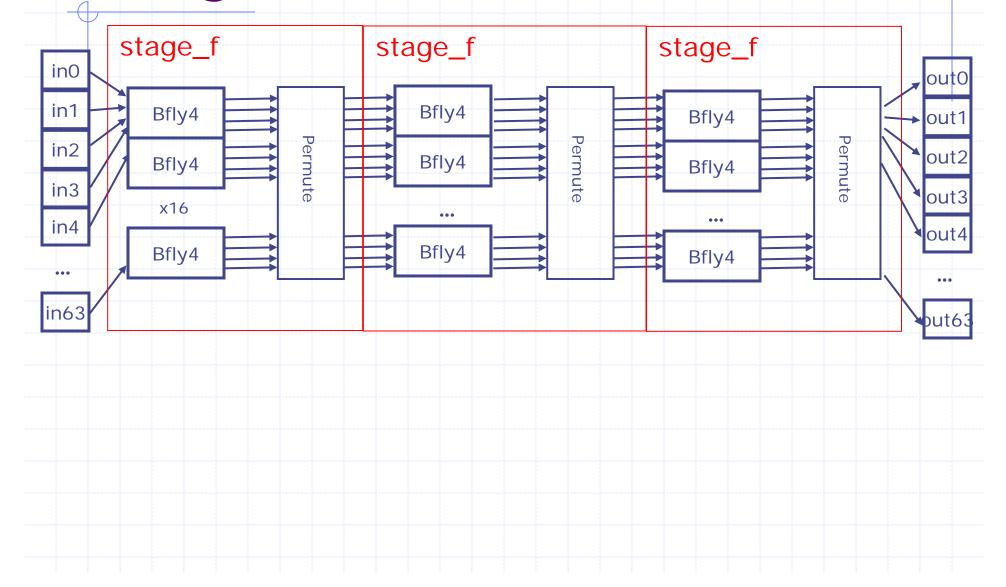

## Stage\_f Function

#### Code for stage\_f

```

function Vector#(64, Complex) stage f

(Bit#(2) stage, Vector#(64, Complex) stage_in);

begin

for (Integer i = 0; i < 16; i = i + 1)

begin

Integer idx = i * 4;

let twid = getTwiddle(stage, fromInteger(i));

let y = bfly4(twid, stage in[idx:idx+3]);

stage_temp[idx] = y[0]; stage_temp[idx+1] = y[1];

stage_temp[idx+2] = y[2]; stage_temp[idx+3] = y[3];

end

//Permutation

for (Integer i = 0; i < 64; i = i + 1)

stage out[i] = stage temp[permute[i]];

end

return(stage out);

18

```

#### Code: Combinational IFFT

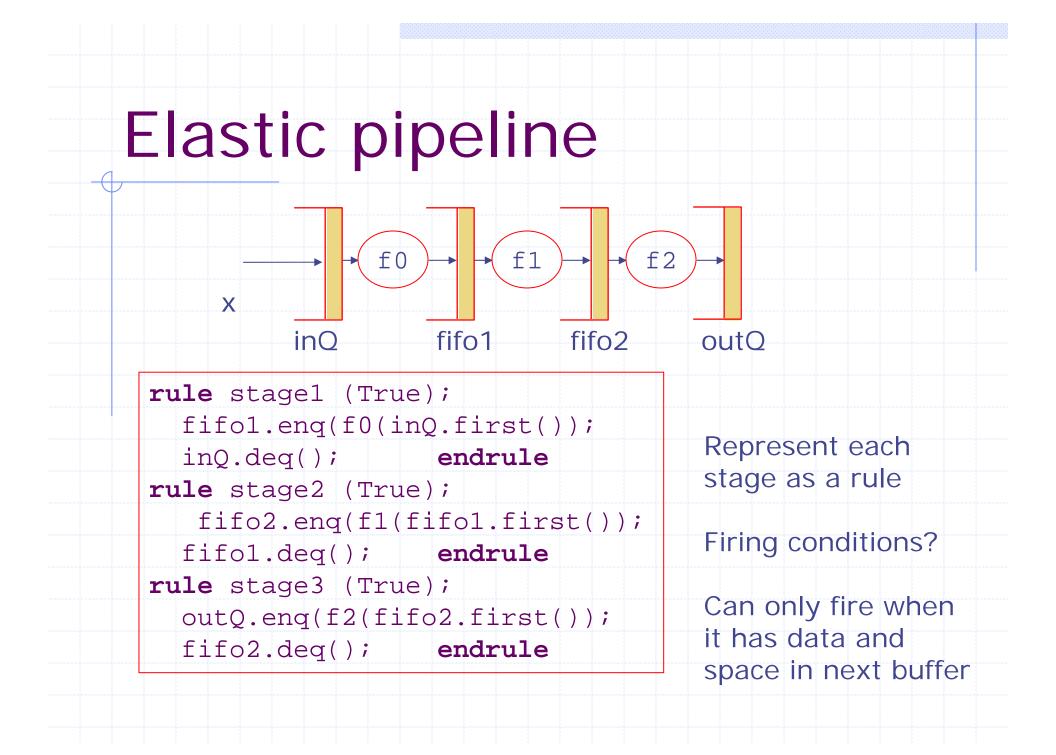

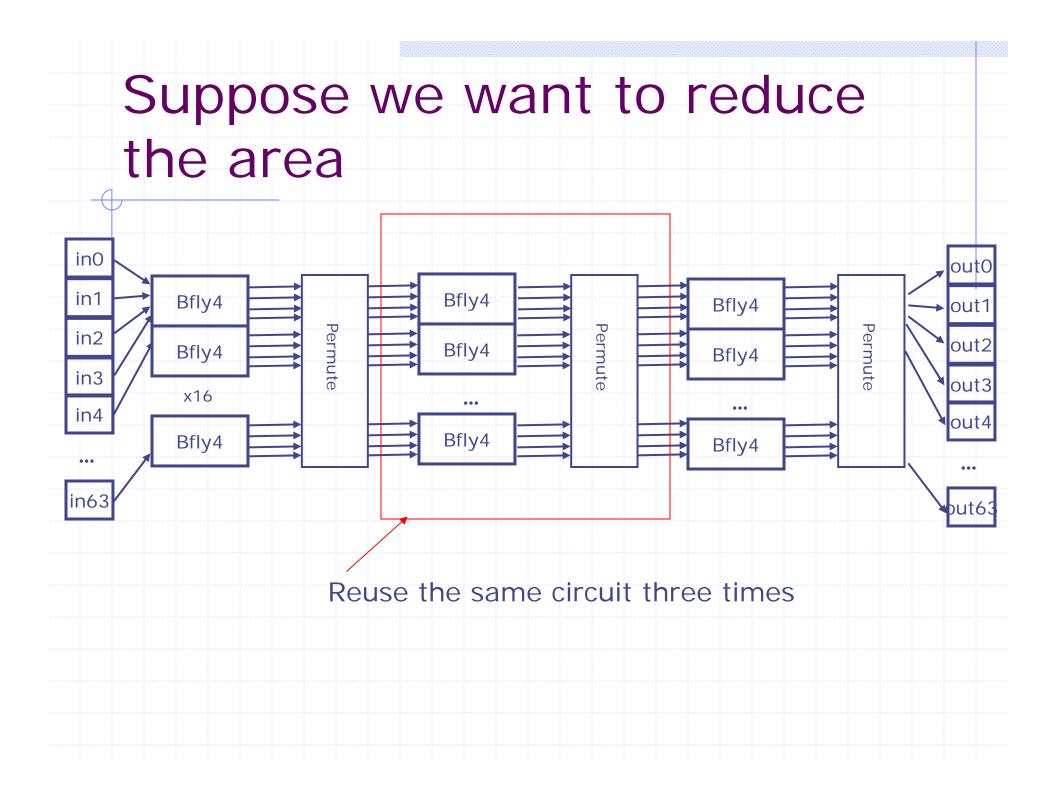

# Suppose we wanted to pipeline the IFFT...

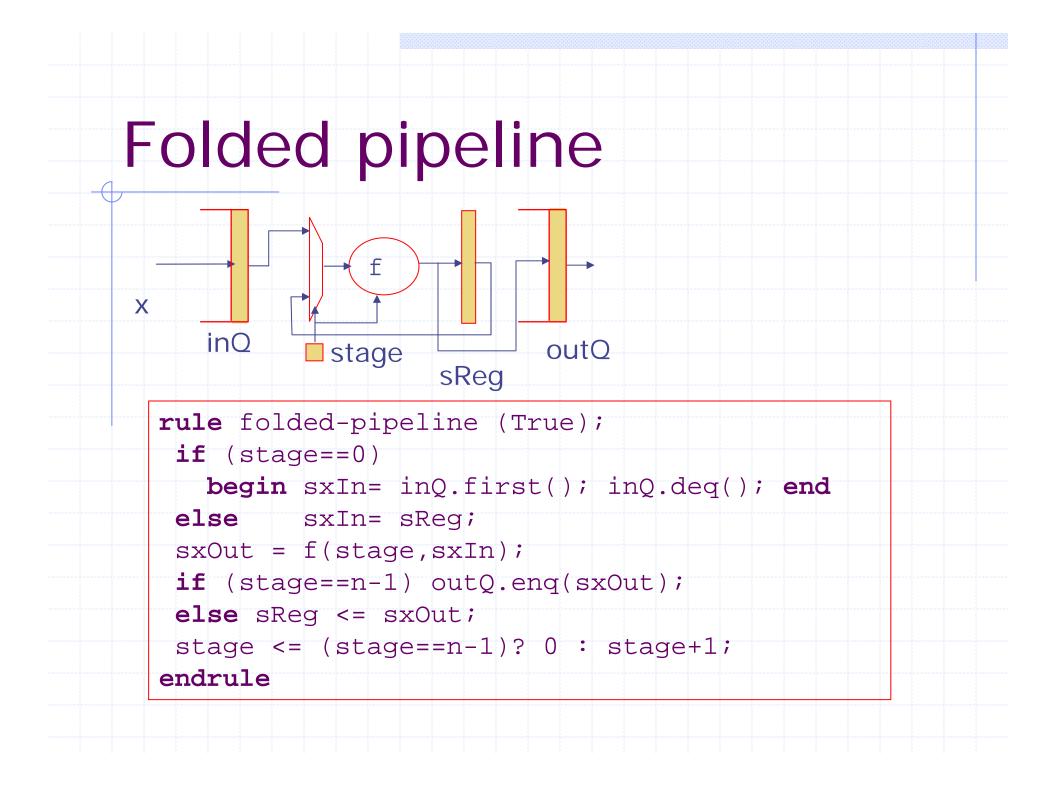

# Dilemma: Designing to the substrate

HW generation is well understood and automatable

- Combinational single-cycle large combinational cloud

- Elastic Pipeline Full throughput pipeline

- Folded Pipeline Multi-cycle FSM

- SW generation from rule is new

- Good conversions from combinational is trivial

- Generating good code from the pipelines is a little tricky (selecting a schedule to factor out bookkeeping operations)

In general different algorithms are more appropriate for hardware than software (or vice versa)

Designers should be aware of these tradeoffs and reason about them as a first-order concern

### **Generating HW**

- Each rule in the design is executed in a single clock cycle

- Convert each rule into (State -> Bool x State) function

- Greedy algorithm to select which rules to fire each cycle:

- Static total ordering of rules

- Must have a total ordering of rules executed

- Considers port resources

As good as hand-written RTL!

## SW Optimizations

- Sequentialization Convert Parallel compositions to sequential ones

- Guard Lifting Exit early on failing executions

- Shadow Minimization higher granularity shadow generation reduces copying

- Shadow Reuse Reuse the same shadow across different rule executions

### Future Work: Scheduling

- Choice of what order to execute rules is a key decision for efficiency

- In HW rules execute in parallel ("free" parallelism)

- In SW, we must balance between:

- Locality Merge rules into larger rule (StreaMITstyle synchronous data flow)

- Thread Parallelism pipeline parallelism

Lots of work remaining (Myron King's PhD)

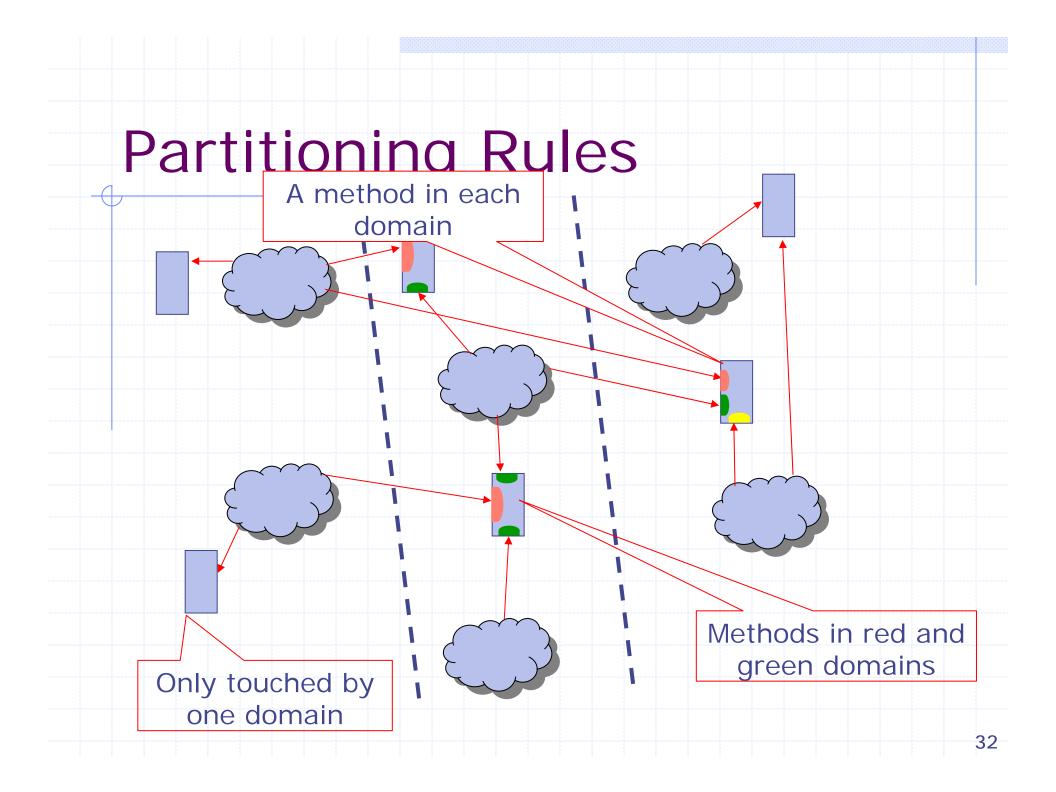

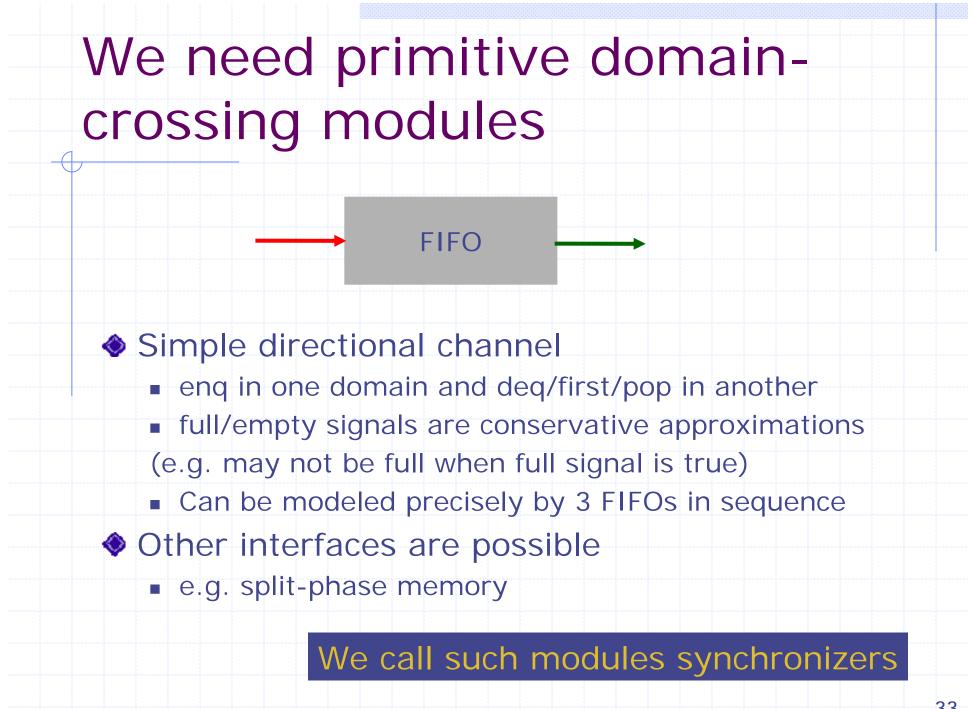

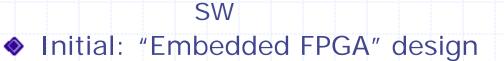

#### **Computational Domains**

Any expression/action can be implemented in either HW or SW

To ease implementation burden and understandability we insist that each rule operates in a single domain

Same follows for methods and expressions

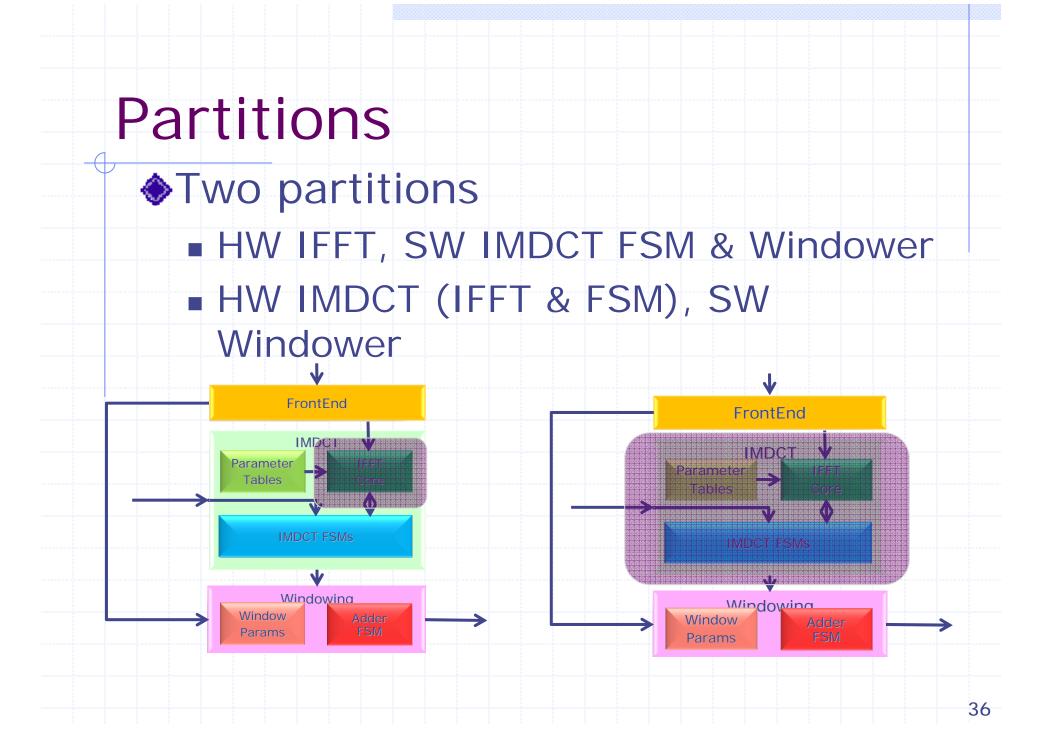

## Partitioning the Ogg Vorbis Example

#### Ogg Vorbis Backend code

```

//State

FIFO#(IMDCTReqData) toimdctQ <- mkFIFO;</pre>

IFFT ifft <- mkIFFT(); Windower window <- mkWindow;

Req icnt <- mkReq(0); Req ocnt <- mkReq(0);

Array iFrame <- mkArray(); Array oFrame <- mkArray();</pre>

//Rules & Methods

method addData(x) = toimdctQ.eng(x);

rule setConfiguration; ... ifft.config... window ...

rule putFrameInIFFT when (icnt < n);

ifft.inputData(iframe[icnt]);

How do we partition

icnt <= icnt+1;</pre>

this?

rule getFrameFromIFFT when (ocnt < n);

rv <- ifft.outputData();</pre>

oframe[ocnt] <= rv;

ocnt <= ocnt+1;</pre>

rule enterWindow(ocnt == n);

window.enter(oframe); ocnt <=0;</pre>

method pcmoutput() = window.getOutput();

```

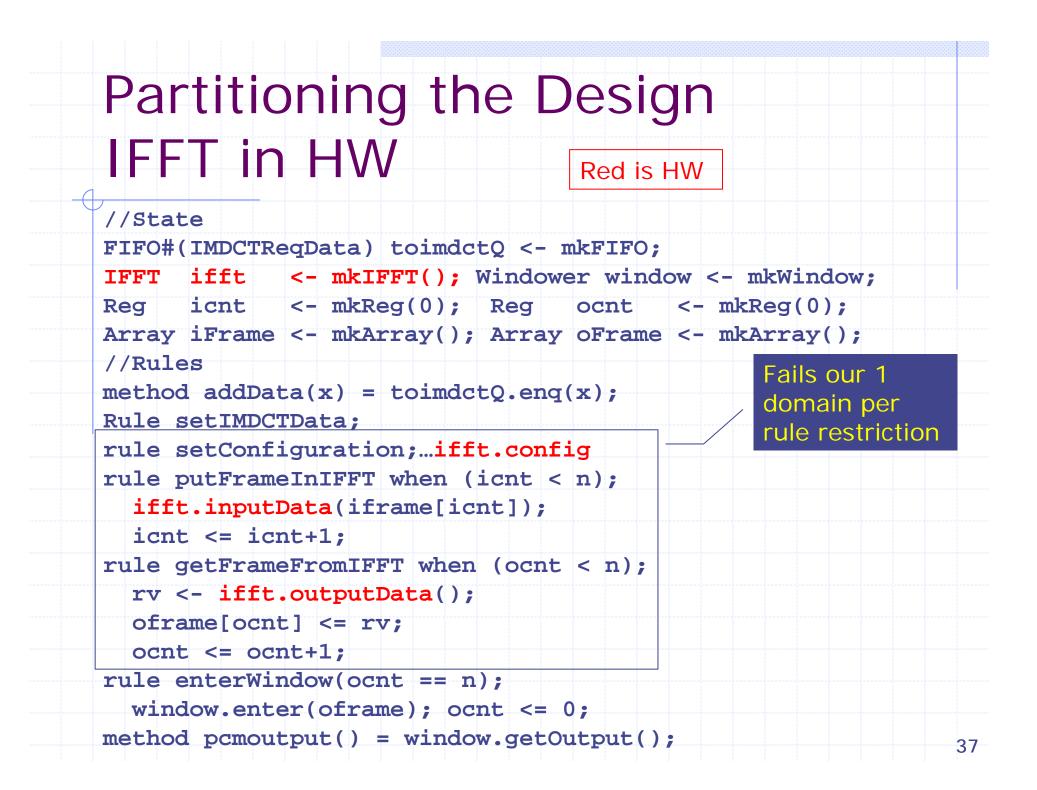

# Making Single Domain Rules IFFT in HW

Synchronizer#(2,1) sync <- mkBusSynchronizer(SW, HW);</pre> rule sendDataToIFFT when (icnt < n); let x <- sync.toHW[0].put(iframe[icnt]);</pre> icnt <= icnt+1;</pre> Add bidirectional rule putFrameInIFFT; synchronizer (2 let x <- sync.toHW[0].get();</pre> virtual channels SW ifft.inputData(x); to HW, 1 HW to rule sendDataFromIFFT(); SW) let v <- ifft.outputData();</pre> sync.toSW[0].put(v); Split rules to fix rule getFrameFromIFFT when (ocnt < n); domain restrictions rv <- sync.toSW[0].get();</pre> oframe[ocnt] <= rv; ocnt <= ocnt+1;</pre> rule setConfigurationSW ... ... sync.toHW[1].put(...)... window.config(...) rule setConfigurationHW ... ... sync.toHW[1].get(...)... ifft.config(...)

# Partitioning the Design IMDCT in HW

//State FIFO#(IMDCTReqData) toimdctQ <- mkFIFO;</pre> IFFT ifft <- mkIFFT(); Windower window <- mkWindow;</pre> Reg icnt <- mkReg(0); Reg ocnt <- mkReg(0);</pre> Array iFrame <- mkArray(); Array oFrame <- mkArray();</pre> //Rules method addData(x) = toimdctQ.enq(x); rule setConfiguration; ... rule setIMDCTData; ... rule putFrameInIFFT when (icnt < n);</pre> ifft.inputData(iframe[icnt]); Breaks icnt <= icnt+1;</pre> Domain rule getFrameFromIFFT when (ocnt < n); Restriction rv <- ifft.outputData();</pre> oframe[ocnt] <= rv;</pre> ocnt <= ocnt+1;</pre> rule enterWindow(ocnt == n); window.enter(oframe); ocnt <=0;</pre> method pcmoutput() = window.getOutput(); 39

# Making Single Domain Rules IMDCT in HW Red is HW

```

//State

Synchronizer#(2,1) sync <- mkBusSynchronizer(SW, HW);</pre>

rule setIMDCTDataSW(hasDatain0)

imdctQ.deq(); sync.toHW[1].put(imdctQ.first);

rule setIMDCTDataHW; ...

Split different

let x <- sync.toHW[1].get(...);</pre>

rules but same

iframe[idx] = ...

procedure

rule setConfigurationSW(hasConfiginQ); ...

sync.toHW[1].put(...);

rule setConfigurationHW; ...

sync.toHW[1].get(...);

rule enterWindowHW(ocnt == n);

sync.toSW[0].put(oframe); ocnt <= 0;</pre>

rule enterWindowSW;

let x <- sync.toSW[0].get();</pre>

window.enter(x);

```

### Making Single Domain Rules

```

Synchronizer#(2,1) sync <- mkBusSynchronizer(SW, HW);</pre>

rule sendDataToIFFT;

let x <- sync.toHW[0].put(iframe[icnt]);</pre>

icnt <= icnt+1;</pre>

rule putFrameInIFFT when (icnt < n);</pre>

let x <- sync.toHW[0].get();</pre>

ifft.inputData(iframe[icnt]);

rule sendDataFromIFFT();

let v <- ifft.outputData();</pre>

sync.toSW[0].put(v);

rule getFrameFromIFFT when (ocnt < n);

rv <- sync.toSW[0].get();</pre>

oframe[ocnt] <= rv;</pre>

Same idea Different

ocnt <= ocnt+1;</pre>

rules need to be split

rule setConfigurationSW ...

... sync.toHW[1].put(...)... window.config(...)

rule setConfigurationHW ...

... sync.toHW[1].get(...)... ifft.config(...)...

```

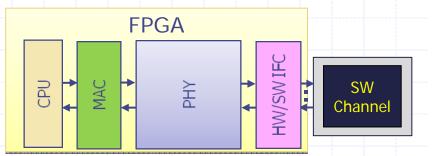

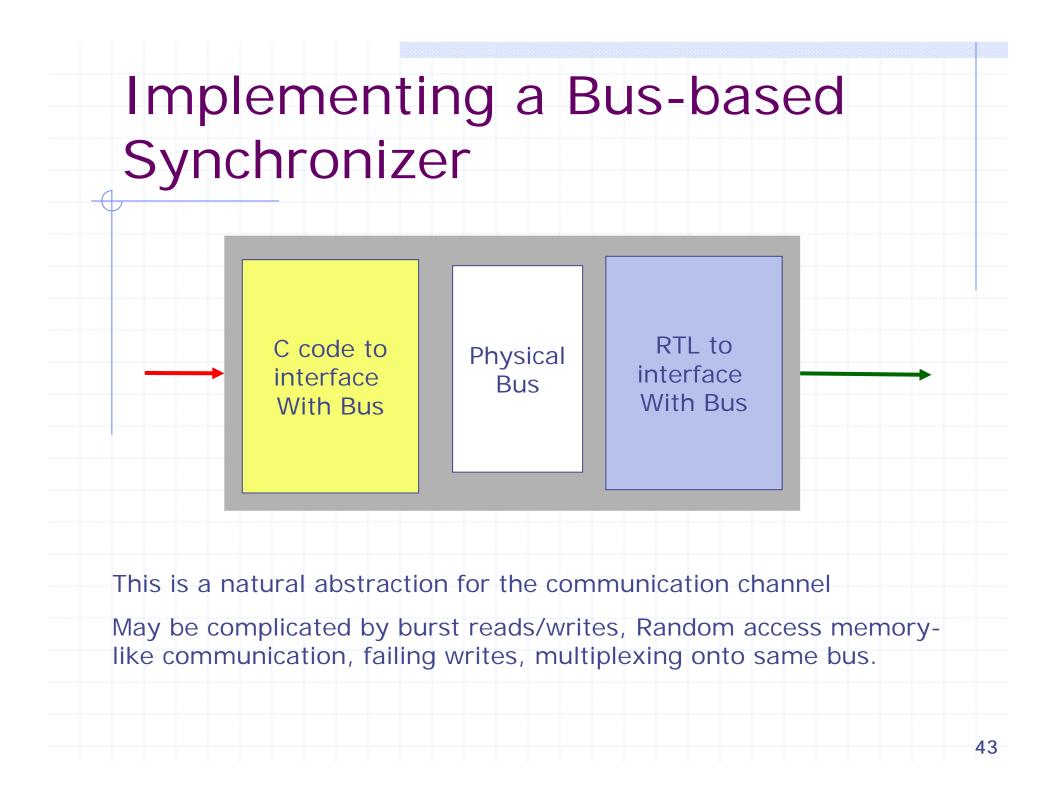

- HW: FPGA

- SW: on FPGA PowerPC

- Communication via Processor Local Bus (PLB)

Sync

HW

- New: Accelerator for General Purpose Processor

- HW: FPGA

- SW: On CPU

- Communication via PCI-Express

- All design specific aspects limited to synchronizer

- Easy to replace. Some variations due to bursts, etc.

# Making it more Complicated: Sharing a Bus Interface

- Solution 3 bus interfaces on the same bus is generally not reasonable

- Large HW cost, redundant

- User can multiplex onto a single synchronizer

- We can represent the Multiplexing logic in BCL directly

- Query: How does this affect performance/correctness?

# Ogg Vorbis Implementations: Platforms

#### FPGA Accelerator

- HW: XUPv5-LX110T FPGA

- SW: 2.8GHz Nehalem Westmere CPU with 3GB of RAM

- Communication: PCI-Express using the Standard Co-Emulation and Modeling Infrastructure (SCE-MI)

#### Embedded System:

- HW: XUPv5-LX110T FPGA

- SW: Microblaze softcore implemented in FPGA

- Communication: point-to-point communication channels called the Fast Simplex Links (FSLs).

## Results

| FrontEnd                  | SW  |      |        |     |     |      |

|---------------------------|-----|------|--------|-----|-----|------|

| IMDCT                     | HW  |      | Hybrid |     | SW  |      |

| Windowing                 | HW  | SW   | Н₩     | SW  | HW  | SW   |

| FPGA Accelerator Platform |     |      |        |     |     |      |

| Speed (s)                 | 8.9 | 28.1 | 84.9   | 102 | 316 | 38.9 |

| FPGA (Regs)               | 36% | 32%  | 40%    | 36% | 34% | 0    |

| FPGA (Slices)             | 22% | 22%  | 20%    | 21% | 23% | 0    |

| Embedded FPGA Platform    |     |      |        |     |     |      |

| Speed (s)                 | 114 | 231  | 414    | 424 | 876 | 896  |

| FPGA (Regs)               | 36% | 35%  | 38%    | 37% | 35% | 33%  |

| FPGA (Slices)             | 36% | 35%  | 33%    | 34% | 37% | 39%  |

All done in a matter of minutes!

3/28/2011

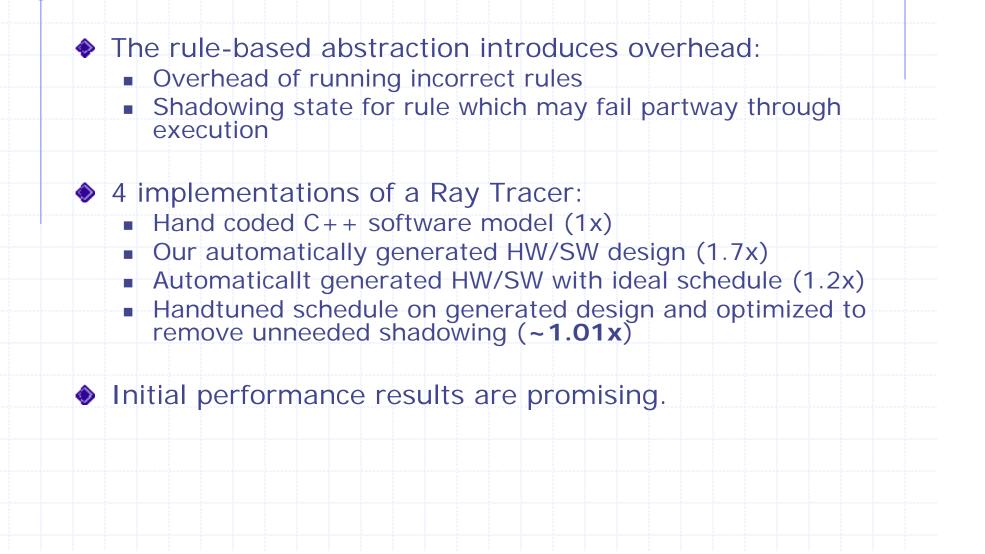

### Software Overhead

The problem with Verification

Formal abstractions are too complicated for most users

Temporal logic spec of a FIFO

Most successes from models with simple abstractions & modularity

- Type checking

- Language-level equivalence (FSM)

Leverage these in the BCL context

# **BCL Verification**

Consider the equivalence of BCL programs

- Can be converted to module equivalence

- BCL is inherently nondeterministic at this level

- Can represent more "spec"-like behavior in the language itself

- Intuitively, we expect to find errors with shorter number of rules executions (minimal trace)

- All the awkwardness of HW/SW timing is abstracted

- Safe over approximation

- Can reach closer to the realized schedule in implementation by representing scheduling as program transform

**KEY: Verifying the actual design**

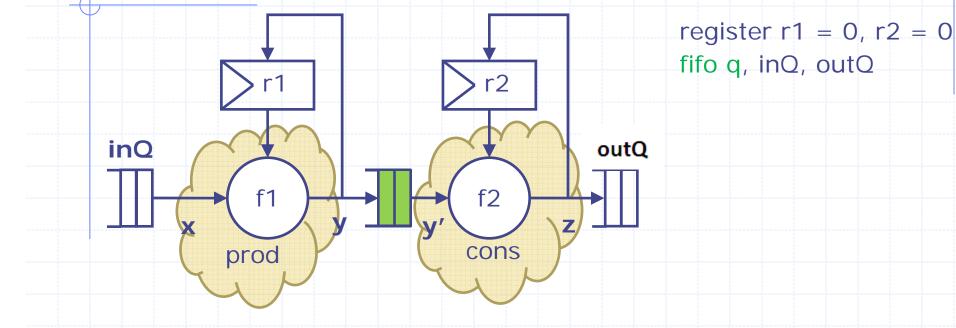

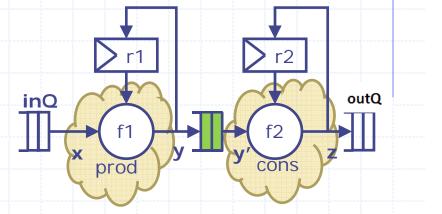

#### Rules for the Refined System

rule produce when

(!q.full && !inQ.empty):

let x = inQ.first;

let y = f1(x,r1);

q.enq(y); inQ.deq;

r1 := y

rule consume when

(!q.empty && !outQ.full):

let y = q.first;

let z = f2(y,r2);

outQ.enq(z); q.deq;

r2 := z;

# Possible executions of the two rule system

rule produce when

(!q.full && !inQ.empty):

let x = inQ.first; let y = f1(x,r1);

q.enq(y); inQ.deq; r1 := y;

rule consume when

(!q.empty && !outQ.full): **let** y = q.first; **let** z = f2(y,r2); outQ.enq(z); q.deq; r2 := z;

Some schedules worth considering:

prod; cons; prod; cons; prod; cons;... prod; prod; cons; prod; cons; prod; cons; ... prod; prod; cons; cons; prod; prod;...

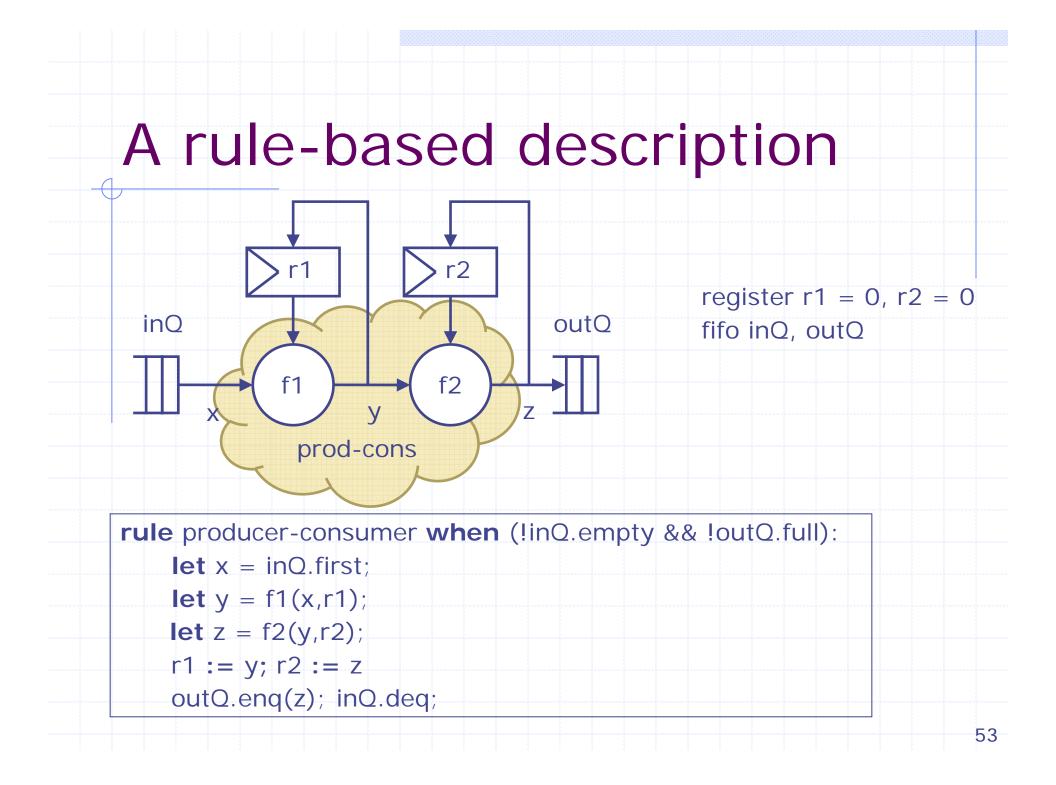

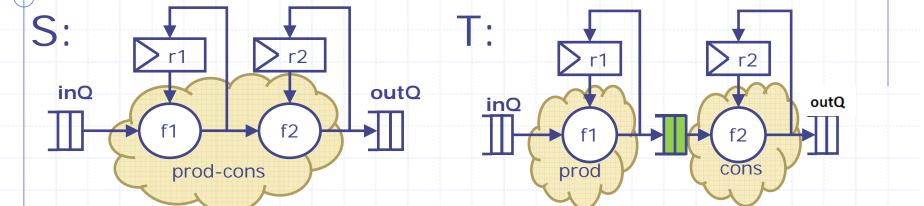

# In what sense are these two systems the same?

rule producer-consumer when (!inQ.empty && !outQ.full): **let** x = inQ.first; **let** y = f1(x,r1);register r1 = 0, r2 = 0**let** z = f2(y,r2);inQ, outQ r1 := y; r2 := z; outQ.enq(z); inQ.deq; same set **Original System** register r1 = 0, r2 = 0of state **Refined System** fifo q, inQ, outQ transitions rule produce when rule consume when (!q.full && !inQ.empty): (!q.empty && !outQ.full): **let** x = inQ.first; **let** y = q.first; **let** y = f1(x,r1);let z = f2(y,r2);q.enq(y); inQ.deq; outQ.enq(z); q.deq; r1 := y r2 := z;

#### When are states equivalent?

If q is empty: the remaining state matches

If q is non-empty: many choices (Run cons, Undo prod, etc.) Tricky to encode in function

Practically, user can only give a partial condition

In our example: (f: T -> S) elides q and is defined only when q is empty.

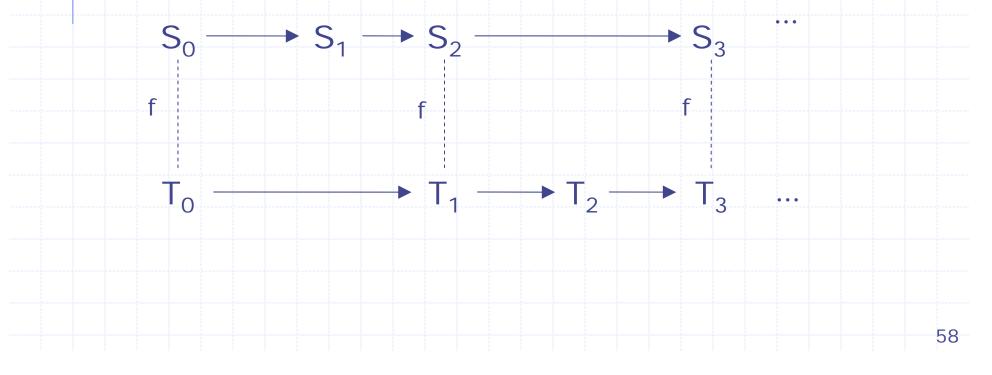

### Equivalence: Intuition

- Programs S and T equal if for each schedule of S, there's a schedule of T where each state that could match, does.

- (i.e. if S reaches a state with a match, then T reaches the corresponding state and vice versa)

#### **Automatic Verification**

This can be verified by coinduction on the schedules

Find finite prefix cover for schedules of T which has a correspondence to a schedule in S

Can be reduced to relatively small set of simple SMT queries

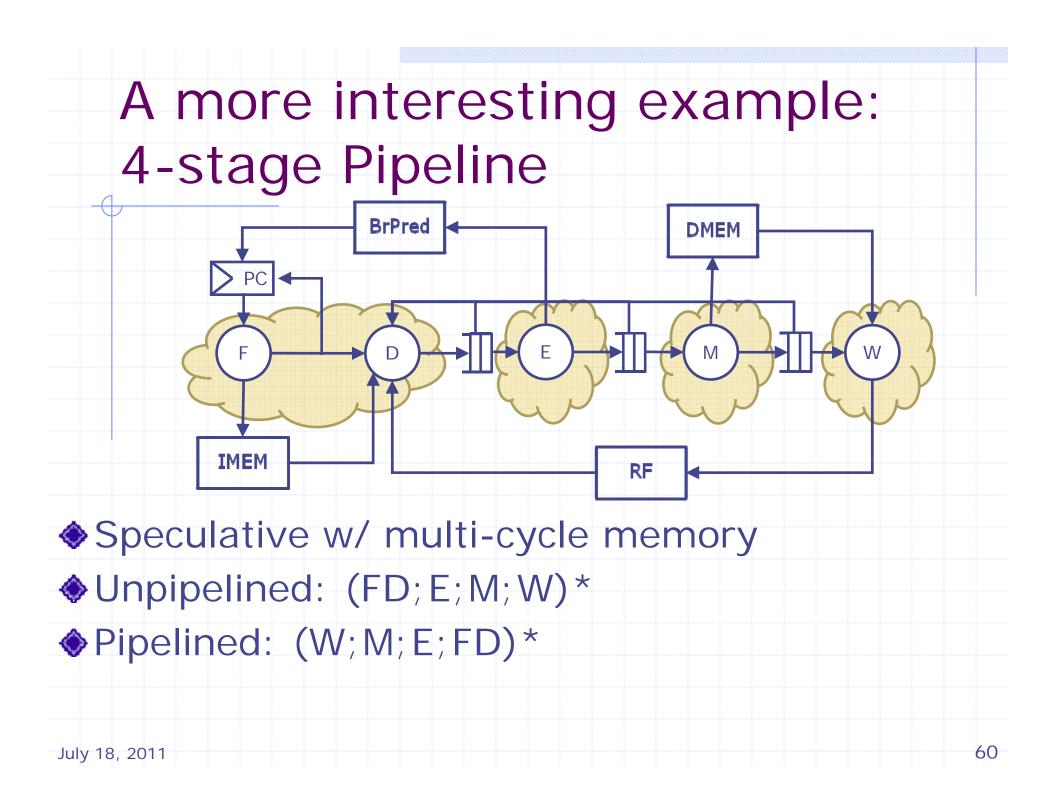

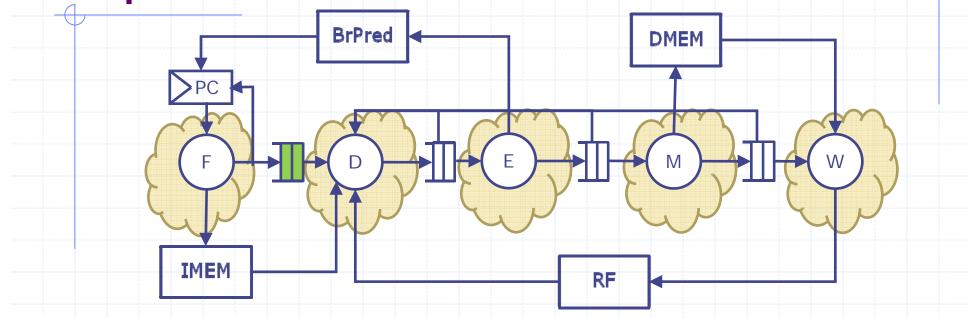

#### Split Fetch and Decode

Initial tool verifies this refinement in a matter of minutes

21 queries considering length 3 prefixes

Can be made much faster (>10x)

## Summary

BCL provides:

- A clean abstraction allowing HW and SW to be unified

- Has enough precision in result to allow the user to partition, evaluate, and tune a design easily.

- HW is already there, SW is within reach

- Provides good abstraction for verification purposes